Part Datasheet Search > Logic ICs > 74LVC573 Datasheet PDF

Images are for reference

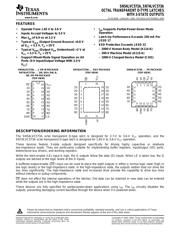

74LVC573 Datasheet PDF

Part Series:

74LVC573 Series

Category:

Logic ICs

Description:

IC OCTAL TRANSPAR LATCH 20-TSSOP

Updated Time: 2023/01/13 03:18:47 (UTC + 8)

74LVC573 Logic ICs Datasheet PDF

74LVC573 Datasheet PDF Logic ICs

21 Pages

NXP

Octal D-type transparent latch with 5V tolerant inputs/outputs 3-State

21 Pages

Philips

Octal D-type transparent latch with 5V tolerant inputs/outputs 3-State

21 Pages

NXP

Octal D-type transparent latch with 5V tolerant inputs/outputs; 3-state

14 Pages

ST Microelectronics

Latch Transparent 3-ST 8CH D-Type 20Pin SOP T/R

Part Datasheet PDF Search

72,405,303 Parts Datasheet PDF, Update more than 5,000 PDF files ervery day.

Relate Parts

Popular Parts Serial

New Parts