Part Datasheet Search > - > CDCP1803 Datasheet PDF

Images are for reference

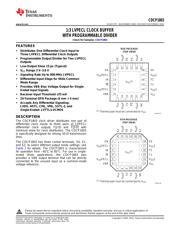

CDCP1803 Datasheet PDF

Part Series:

CDCP1803 Series

Category:

-

Description:

The CDCP1803 clock driver distributes one pair of differential clock inputs to three pairs of LVPECL differential clo...

Updated Time: 2023/01/13 03:35:25 (UTC + 8)

CDCP1803 - Datasheet PDF

CDCP1803 Datasheet PDF -

25 Pages

TI

The CDCP1803 clock driver distributes one pair of differential clock inputs to three pairs of LVPECL differential clo...

Part Datasheet PDF Search

72,405,303 Parts Datasheet PDF, Update more than 5,000 PDF files ervery day.